# EMBER® EM35x NCP Host (STM32) Module Technical Specification

When combined with an Ember EM35x NCP Breakout Board, the Ember STM32 NCP Host Module offers a complete ZigBee wireless solution for development and deployment of a low-data-rate, low-power ZigBee application. The STM32 microprocessor is part of the two-layer (FR4-based) host module that connects to the EM35x NCP Breakout Board through the board-to-board connectors.

This document provides the technical specification for the STM32 EM35x NCP Host Module. It describes the board-level interfaces as well as the key performance parameters. In addition, it provides the necessary information for developer to validate their application designs using the STM32 EM35x NCP Host Module.

#### **New in This Revision**

Document renumbering.

#### **Contents**

| 1 | STN        | M32 Host Module Features                             | . 2 |  |  |

|---|------------|------------------------------------------------------|-----|--|--|

|   | Components |                                                      |     |  |  |

|   |            | STM32 Microcontroller                                |     |  |  |

|   |            | EM35x NCP Breakout Board interface connector (J1-J2) |     |  |  |

|   |            | JTAG Programming and Debug Connector (J3)            |     |  |  |

|   |            | Unused STM32 GPIO (TP0-TP10)                         |     |  |  |

|   |            | M32 NCP Host Module Schematic                        |     |  |  |

#### 1 STM32 Host Module Features

The STM32 EM35x NCP Host Module offers:

- ARM<sup>®</sup> Cortex<sup>™</sup>-M3 based microprocessor (STM32F103RET6)

512 kB FLASH, 64 kB RAM

- Host UART1 for use with STM32 serial bootloader and application serial UART

- Host UART2 for EZSP UART interface to EM35x NCP

- Host SPI1 for EZSP SPI interface to EM35x NCP

- 16 additional Host GPIO routed to mating connector for application use on EM35x NCP Breakout Board

- All unused Host GPIO routed to test points

- 14-pin, 0.1" pitch, dual-row, JTAG programming and debug header (could be used with a JTAG programmer such as SEGGER's JLINK.)

- 16-pin, 0.1" pitch, single-row along with a 20-pin 0.1" pitch, single-row, board-to-board connector for mating to the EM35x NCP Breakout Board

- Spare Host IO routed to test points for application use

Table 1 lists the DC electrical characteristics of the STM32 EM35x NCP Host Module.

**Table 1. DC Electrical Characteristics**

| Parameter             | Min. | Тур. | Max. | Unit |

|-----------------------|------|------|------|------|

| VDD supply            | 2.0  |      | 3.6  | V    |

| Current Draw (active) |      | 45   |      | mA   |

| Operating temperature | 0    |      | + 55 | С    |

For more information on the STM32F103RET6, refer to the STM32 data sheet (download from <a href="http://www.st.com/internet/mcu/product/164485.jsp">http://www.st.com/internet/mcu/product/164485.jsp</a>).

# 2 Components

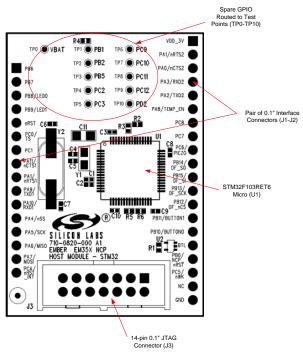

Figure 1 illustrates the components on layer 1 (top side), while Figure 2 illustrates the components on layer 2 (bottom side).

Figure 1. Assembly Print for Layer 1

Figure 2. Assembly Print for Layer 2

Rev. 0.4 3

#### 2.1 STM32 Microcontroller

The STM32 NCP Host Module contains the STM32F103RET6 microcontroller from ST Microelectronics. This microcontroller is based on the Cortex-M3 core from ARM. This version of the STM32 contains 512 kB of FLASH and 64 kB of SRAM. Two USARTs are exposed to the board-to-board connector for STM32 system bootloading (STM32 USART1) and EZSP UART (STM32 USART2) to the EM35x NCP. Two SPI ports are also routed to the board-to-board connector for EZSP SPI interface to the EM35x NCP (STM32 SPI1) and external DataFlash (STM32 SPI2). Various other IOs are exposed to the board-to-board connector, including timers and interrupts. For more information on the STM32F103RET6, refer to the STM32 datasheet (download from <a href="http://www.st.com/internet/mcu/product/164485.jsp">http://www.st.com/internet/mcu/product/164485.jsp</a>).

# 2.2 EM35x NCP Breakout Board interface connector (J1-J2)

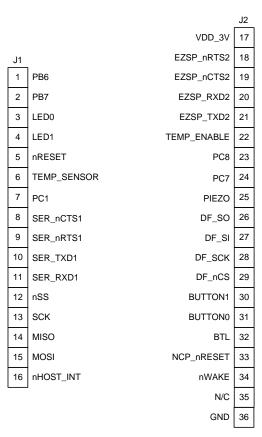

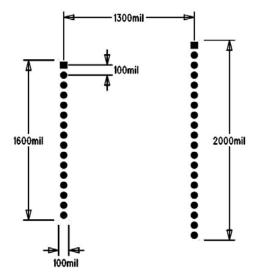

Two single-row, 0.1" pitch, connectors make up the STM32 NCP host module interface to the EM35x NCP Breakout Board. The board-to-board connector scheme allows access to 16 Host GPIO for application purposes, along with 2 USART ports and 1 SPI port dedicated to EZSP and debug use. These 16 Host GPIO are listed in Table 2; the connector is illustrated in Figure 3. Interface connector dimensions are shown in Figure 4.

| Host GPIO | STM32 I/O | Primary GPIO Function                   |

|-----------|-----------|-----------------------------------------|

| HGPIO0    | PB8       | Application LED (LED0)                  |

| HGPIO1    | PB9       | Application LED (LED1)                  |

| HGPIO2    | PB10      | Application Button (BUTTON0)            |

| HGPIO3    | PB11      | Application Button (BUTTON1)            |

| HGPIO4    | PC6       | Application Speaker (PIEZO)             |

| HGPIO5    | PC7       | Spare GPIO                              |

| HGPIO6    | PC8       | Spare GPIO                              |

| HGPIO7    | PA8       | Temperature Sensor Enable (TEMP_ENABLE) |

| HGPIO8    | PC0       | Temperature Sensor ADC (TEMP_SENSOR)    |

| HGPIO9    | PC1       | Spare GPIO                              |

| HGPIO10   | PB6       | Spare GPIO                              |

| HGPIO11   | PB7       | DataFlash Shutdown (DF_nSD)             |

| HGPIO12   | PB12      | DataFlash SPI Chip Select (DF_nCS)      |

| HGPIO13   | PB13      | DataFlash SPI Clock (DF_SCK)            |

| HGPIO14   | PB15      | DataFlash SPI Serial In (DF_SI)         |

| HGPIO15   | PB14      | DataFlash SPI Serial Out (DF_SO)        |

**Table 2. Host GPIO Functions**

4 Rev. 0.4

Figure 3. Board-to-Board Connector for the STM32 NCP Host Module

Figure 4. Board-to-Board Connector Dimensions for the STM32 NCP Host Module

Table 3 describes the pinout and signal names at J1 and J2.

For more information on the functions of the STM32 GPIO, refer to the STM32 datasheet (download from <a href="http://www.st.com/internet/mcu/product/164485.jsp">http://www.st.com/internet/mcu/product/164485.jsp</a>).

Rev. 0.4 5

Table 3. Pinout and signal names of the interface connectors

| Pin# | Signal name | Direction <sup>2</sup> | Connector | Description                        |

|------|-------------|------------------------|-----------|------------------------------------|

| 1    | PB6         | I/O                    | J1        | Spare STM32 GPIO (HGPIO10)         |

| 2    | PB7         | I/O                    | J1        | Spare STM32 GPIO (HGPIO11)         |

| 3    | LED0        | I/O                    | J1        | STM32 PB8 (HGPIO0)                 |

| 4    | LED1        | I/O                    | J1        | STM32 PB9 (HGPIO1)                 |

| 5    | nRESET      | I/O                    | J1        | STM32 Reset                        |

| 6    | TEMP_SENSOR | I/O                    | J1        | STM32 PC0 (HGPIO8)                 |

| 7    | PC1         | I/O                    | J1        | Spare STM32 GPIO (HGPIO9)          |

| 8    | SER_nCTS1   | I/O                    | J1        | STM32 PA11                         |

| 9    | SER_nRTS1   | I/O                    | J1        | STM32 PA12                         |

| 10   | SER_TXD1    | I/O                    | J1        | STM32 PA9                          |

| 11   | SER_RXD1    | I/O                    | J1        | STM32 PA10                         |

| 12   | nSS         | I/O                    | J1        | STM32 PA4                          |

| 13   | SCK         | I/O                    | J1        | STM32 PA5                          |

| 14   | MISO        | I/O                    | J1        | STM32 PA6                          |

| 15   | MOSI        | I/O                    | J1        | STM32 PA7                          |

| 16   | nHOST_INT   | I/O                    | J1        | STM32 PC4                          |

| 17   | VDD_3V      | Power                  | J2        | 3V Source Pin                      |

| 18   | EZSP_nRTS2  | I/O                    | J2        | STM32 PA1                          |

| 19   | EZSP_nCTS2  | I/O                    | J2        | STM32 PA0-WKUP                     |

| 20   | EZSP_RXD2   | I/O                    | J2        | STM32 PA3                          |

| 21   | EZSP_TXD2   | I/O                    | J2        | STM32 PA2                          |

| 22   | TEMP_ENABLE | I/O                    | J2        | STM32 PA8 (HGPIO7)                 |

| 23   | PC8         | I/O                    | J2        | Spare STM32 GPIO (HGPIO6)          |

| 24   | PC7         | I/O                    | J2        | Spare STM32 GPIO (HGPIO5)          |

| 25   | PIEZO       | I/O                    | J2        | STM32 PC6 (HGPIO4)                 |

| 26   | DF_SO       | I/O                    | J2        | STM32 PB14 (HGPIO15)               |

| 27   | DF_SI       | I/O                    | J2        | STM32 PB15 (HGPIO14)               |

| 28   | DF_SCK      | I/O                    | J2        | STM32 PB13 (HGPIO13)               |

| 29   | DF_nCS      | I/O                    | J2        | STM32 PB12 (HGPIO12)               |

| 30   | BUTTON1     | I/O                    | J2        | STM32 PB11 (HGPIO3)                |

| 31   | BUTTON0     | I/O                    | J2        | STM32 PB10 (HGPIO2)                |

| 32   | BTL         | I                      | J2        | Inverted and routed to STM32 BOOT0 |

| 33   | NCP_nRESET  | I/O                    | J2        | STM32 PB0                          |

| 34   | nWAKE       | I/O                    | J2        | STM32PC5                           |

| 35   | NC          | N/A                    | J2        | Not connected                      |

| 36   | GND         | Power                  | J2        | Ground connection                  |

<sup>&</sup>lt;sup>2</sup> with respect to the STM32

# 2.3 JTAG Programming and Debug Connector (J3)

The STM32 NCP Host module includes a 14-pin 0.1" dual-row header for JTAG programming and debug access. Figure 5 shows the pinout of this header. Note that the EM35x NCP Kit does not ship with a programmer that interfaces to this header. Third-party programmers may connect to this header. For example, the J-Link ARM 14-

6 Rev. 0.4

pin Adapter from SEGGER (<a href="http://www.segger.com/cms/jlink-adapters.html#14pinAdapter">http://www.segger.com/cms/jlink-adapters.html#14pinAdapter</a>) may be connected directly to this header.

Figure 5. JTAG Connector Pinout (J3)

## 2.4 Unused STM32 GPIO (TP0-TP10)

The STM32 NCP Host module routes all GPIO not routed to the mating connectors to test points TP0 through TP10. This allows the developer to utilize all STM32 GPIO for their application, if required. Table 4 lists these test points.

**Test Point** Signal name **Test Point** Signal name TP0 **VBAT** TP6 PC9 TP1 PB1 TP7 PC10 TP2 PB2\_BOOT1 TP8 PC11 TP3 PB5 TP9 PC12 TP4 PC2 TP10 PD2 TP5 PC3

Table 4. STM32 Unused GPIO Routed to Test Points

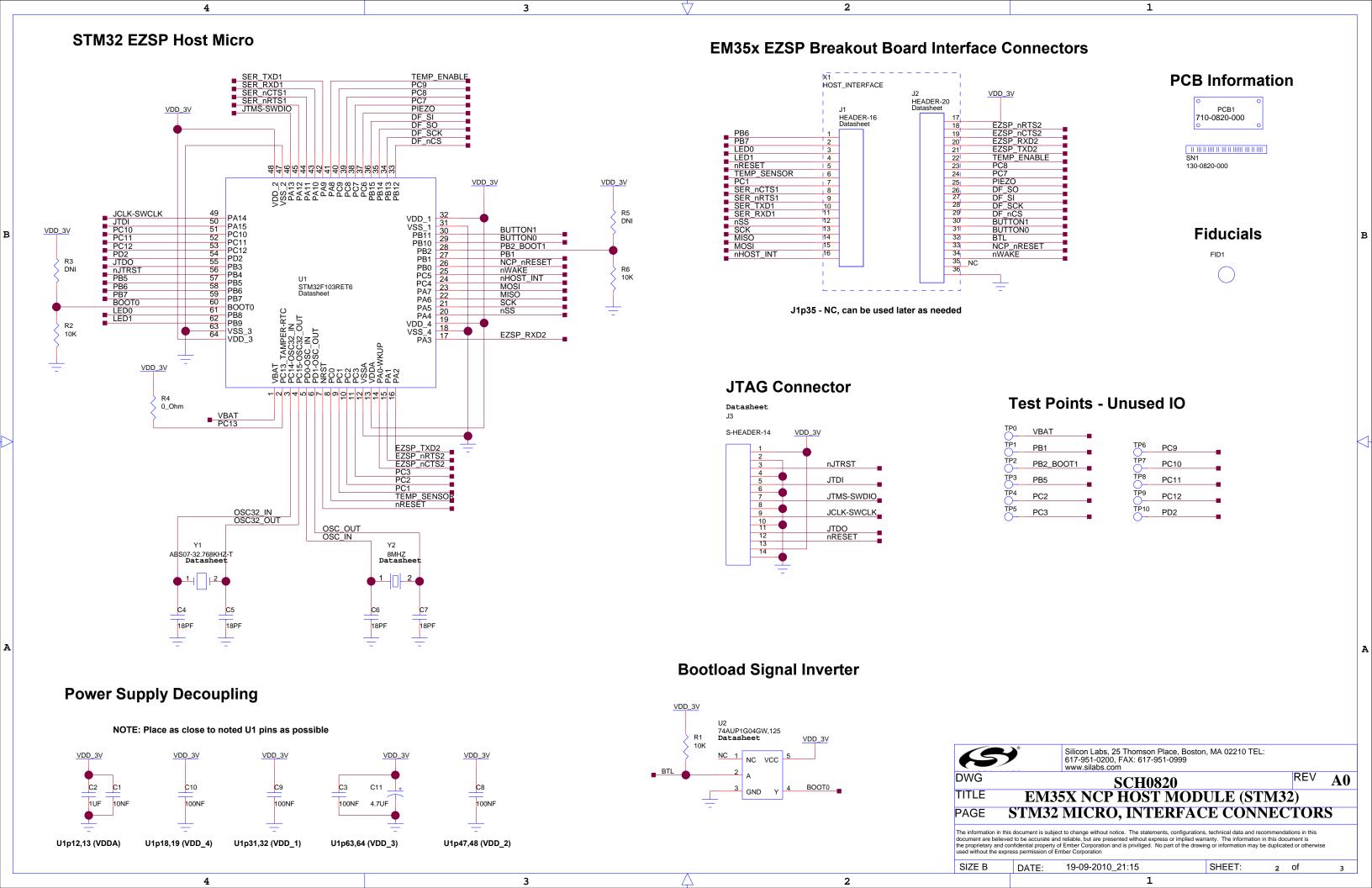

### 3 STM32 NCP Host Module Schematic

The STM32 NCP Host Module schematic is included at the end of this document.

Rev. 0.4 7

# EM35x NCP Host Module (STM32)

| Sheet | Details                           |

|-------|-----------------------------------|

| 1     | COVER SHEET                       |

| 2     | STM32 MICRO, INTERFACE CONNECTORS |

| 3     | PEVISION NOTES                    |

#### SCHEMATIC NOTES:

- -- Version P0 --\*Released: 2010-06-11

- \*Initial version released, Version PO (initial draft)

- -- Version P1 --\*Released: 2010-08-03 \*Changes from P0 to P1:

- 1) Swapped UART1 with UART2 on X1 (J1, J2).

- 2) Changed R2 from 0 ohm to 10k ohm.

- 3) Changed R6 from DNI to 10k ohm.

- Changed U1.27 net connection from BTL to PB1.

- 5) Change TP1 to TP0 for VBAT net.

- 6) Added TP1 for PB1 net.

- 7) Added inverter IC U2 for inverting BTL net for connection to BOOTO net.

- -- Version A0 --

- \*Released: 2010-09-20

- \*Production version release

- \*Changes from P1 to A0:

- Removed DS1 and R1 for lowest current capability.

Renamed UART1 nets to SER\_TXD1, etc.

- 3) Renamed UART2 nets to EZSP\_TXD1, etc.

4) Added 10k pull-up R7 to U2 BTL net.

- 5) Updated title from EZSP to NCP.

- 6) Corrected DF SO/ SI error at X1 J2p26/27 (reversed).

- 7) Removed Packet Trace Port connector footprint J4.

- 8) Replaced J3 with 14-pin 0.1" JTAG connector.

#### PCB LAYOUT NOTES:

- -- Version P0 --

- \*Released: 2010-06-11

- \*Initial version released, Version PO (initial draft)

- -- Version P1 --

- \*Released: 2010-08-03

- \*Changes from P0 to P1:

- 1) Added Inverter IC U2.

- 2) Re-routed UART1 and UART2 nets.

- 3) Added missing test points from PO version.

- -- Version A0 --

- \*Released: 2010-09-20

- \*Changes from P1 to A0:

- \*Production version release

- 1) All schematic notes reflected in layout.

Silicon Labs, 25 Thomson Place, Boston, MA 02210 TEL: 617-951-0200, FAX: 617-951-0999

www.silabs.com

**SCH0820**

$\mathsf{REV}\,\mathbf{A0}$

В

Α

TITLE

EM35X NCP HOST MODULE (STM32)

PAGE **REVISION NOTES**

The information in this document is subject to change without notice. The statements, configurations, technical data and recommendations in this document are believed to be accurate and reliable, but are presented without express or implied warranty. The information in this document is the proprietary and confidential property of Ember Corporation and is priviliged. No part of the drawing or information may be duplicated or otherwise used without the express permission of Ember Corporation

SIZE A

DATE:

19-09-2010\_21:15

SHEET:

of

3

# **TS10**

#### **CONTACT INFORMATION**

Silicon Laboratories Inc.

400 West Cesar Chavez Austin, TX 78701 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032

Please visit the Silicon Labs Technical Support web page for ZigBee products: www.silabs.com/zigbee-support and register to submit a technical support request

#### **Patent Notice**

Silicon Labs invests in research and development to help our customers differentiate in the market with innovative low-power, small size, analog-intensive mixed-signal solutions. Silicon Labs' extensive patent portfolio is a testament to our unique approach and world-class engineering team.

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories, Silicon Labs, and Ember are registered trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

8 Rev. 0.4